신기술 동향

다른 기사 보기

신개념 뉴로모픽 컴퓨팅을 위한 3단자 시냅스 소재 및 소자

기고자. 울산과학기술원 신소재공학과 윤태식 교수1. 서론

빅데이터 컴퓨팅을 위한 신개념 뉴로모픽 컴퓨팅

인공지능, 사물인터넷, 자율 주행차, 로봇 시스템 등 4차 산업의 핵심 기술 특징은 대용량 데이터를 바탕으로 하는 지능형 시스템이라는 점이다. 이러한 시스템을 구현하기 위해서 대용량 데이터를 높은 에너지 효율로 실시간 처리할 능력을 갖춘 고성능 고효율 컴퓨팅 시스템의 필요성이 증대되고 있다. 인공지능 시스템은 대용량 데이터를 바탕으로 학습과 추론 등의 다양한 두뇌 모사 지능형 동작을 나타내도록 요구되고 있고, 자율 주행차는 안정적인 구동을 위해 주변 센서로부터 확보한 데이터를 외부 서버에 전송하지 않고 실시간으로 처리하는 것이 필요하다. 따라서, 이를 위해서는 저전력, 고에너지 효율, 고성능, 고속 데이터 처리 능력을 갖춘 컴퓨팅 시스템이 필요하게 된다.

현재까지 주로 활용되는 고성능 컴퓨팅 시스템은 폰 노이만(von Neumann) 아키텍처, 즉 프로세서와 메모리 소자가 분리된 아키텍처를 기반으로 개발되어 왔다. 이는 프로세서가 메모리로부터 데이터를 받아 정보를 처리하고 그 결과를 다시 메모리에 저장하는 방식으로 동작한다. 이러한 동작 방식은 대용량 데이터를 처리함에 있어 '폰 노이만 병목현상(von Neumann bottle neck)'이라 불리는 신호 지연에 의한 성능 저하와 막대한 전력 소모 문제를 안고 있다. 또한, 폰 노이만 시스템은 단순 계산 능력은 우수한 반면, 대량의 복잡하고 비구조화된 데이터를 처리하는 환경, 즉 인공지능과 같이 대용량 데이터를 처리해야 하는 최신 응용 시스템에 적용하기에 한계가 있다. 본고에서는 이러한 빅데이터 환경에 적합한 컴퓨팅 시스템으로 연구·개발되고 있는 뉴로모픽 컴퓨팅의 핵심 요소인 인공 시냅스 소자로서 3단자 구조를 갖는 인공 시냅스 소재 및 소자 기술에 대해 소개하고자 한다.

2. 메모리 기반 3단자 시냅스 소재 및 소자

대용량 데이터를 효과적으로 처리할 수 있는 컴퓨팅 시스템을 구현하기 위해서는 프로세서의 성능개선과 더불어 메모리 소자의 발전이 동시에 이루어져야 한다. 즉, 대용량 데이터 저장을 위한 고용량 메모리 개발, 폰 노이만 아키텍처의 한계를 극복하기 위하여 연산 과정에서 외부 데이터 접근을 최소화할 수 있도록 일부의 데이터를 연산 장치와 통합한 임베디드 메모리 용량 및 성능 개선, 메모리에서 데이터를 처리하는 프로세싱 인 메모리(processing-in-memory) 개발, 높은 에너지 효율과 저전력 두뇌모사 기능을 갖는 뉴로모픽 시스템의 시냅스 향 메모리 개발이 필요하다. 이러한 모든 시스템에 공통적으로 요구되는 메모리 요건은 고성능, 대용량, 저전력 구동으로 요약할 수 있다. 또한, 뉴로모픽 시스템 적용을 위해서는 생체 시냅스의 거동까지 모사할 수 있는 메모리 특성을 구현하는 것이 요구된다.

3단자 시냅스 소자의 특징과 장점

대용량, 고성능, 저전력 메모리 및 시냅스 소자로서 저항변화, 상변화, 강유전체, 자성 소재 등을 활용한 2단자 소자와 더불어, 트랜지스터 구조를 갖는 3단자 소자 연구가 활발히 진행되고 있다. 2단자 소자는 3단자 소자에 비해 간단한 구조를 갖고 있으므로 고집적 어레이로 제작하여 높은 집적도를 구현하는 데 용이한 장점이 있다. 하지만, 현재 가장 높은 집적도를 나타내고 있는 수직형 NAND 플래시와 같이 3차원 수직형 소자를 제작하는 데 필요한 공정 기술 및 아키텍처 기술이 적절하게 제시되고 있지 못한 상황이다. 또한, 2단자 소자에서는 양단 간의 전압 차에 의해 쓰기, 지우기, 읽기 동작을 모두 수행해야 함으로 동작 조건에 제한이 있고, 읽기 과정에서 메모리 상태(시냅스 가중치)의 변화(read disturbance)와 같은 신뢰성 문제를 더욱 개선해야 하는 상황이다. 특히, 시냅스 가중치 업데이트(학습)와 시냅스 가중치 읽기(추론) 동작을 동시에 수행하기에 어려운 단점이 있다.

반면, 3단자 소자는 소스(source), 드레인(drain), 게이트(gate) 전극으로 이루어진 트랜지스터이면서 동시에 메모리 기능을 갖고 있다. 3단자로 구성되어 있으므로, 프로그래밍 또는 시냅스 소자의 시냅스 가중치(채널 전도도)를 갱신하는 학습 동작과 가중치를 이용한 연산, 추론 동작을 독립적으로 수행할 수 있다는 장점이 있다. 즉, 소스와 드레인 전극에 인가된 전압에 의해 연산, 추론 동작을 하면서, 게이트 전압으로 트랜지스터의 채널 전도도인 시냅스 가중치를 변화시키는 학습 동작을 간섭 없이 수행하는 것이 가능하므로 더 유연한 동작이 가능하다. 그리고, 연산, 추론 등의 신호 처리 과정에서 기억 상태가 변하는 간섭 문제를 최소화하여 안정적인 기억 기능을 구현할 수 있다는 장점이 있다. 3단자 시냅틱 트랜지스터의 경우, 드레인 전압뿐만 아니라 게이트 전압에 의해서도 시냅스 가중치에 해당하는 채널 전도도가 결정됨으로 광대역 가중치 확보, 선형적 및 대칭적 가중치 변화 구현에 용이하며, 트랜지스터의 스위칭 기능을 활용하여 추가로 선택 소자 없이 어레이 구조에서의 누설 전류(sneak path leakage)를 최소화할 수 있다.

다양한 3단자 시냅스 소재 및 소자

3단자 소자에서 시냅스 가중치의 변화를 구현하기 위해서는 3단자 소자의 채널 전도도를 비휘발적으로 변화시킬 수 있어야 한다. 대표적인 대용량 비휘발성 메모리인 플래시 메모리는 3단자 트랜지스터의 게이트 절연막 내부에 형성된 전하 저장층 내부에 전하를 저장함에 따른 문턱전압의 이동을 이용한 소자이다. 문턱전압 이동을 통해 읽기 전압에서 채널에 전류가 흐르는 경우와 흐르지 않는 경우를 구별하여 메모리 소자로 구동하는 것이다. 이는 채널 전도도를 '0'과 '1'의 디지털 형태로 구별하여 메모리 상태를 구별하는 소자라고 할 수 있다. 이와 같이, 채널 전도도를 변화시킬 수 있다면, 특히 멀티레벨 또는 아날로그 형태로 변화시켜서 이를 시냅스 가중치 변화로 활용하는 소자가 3단자 시냅스 소자라고 할 수 있다. 3단자 시냅스 소자의 채널 전도도를 변화시키는 다양한 방법을 소개하면 다음과 같다.

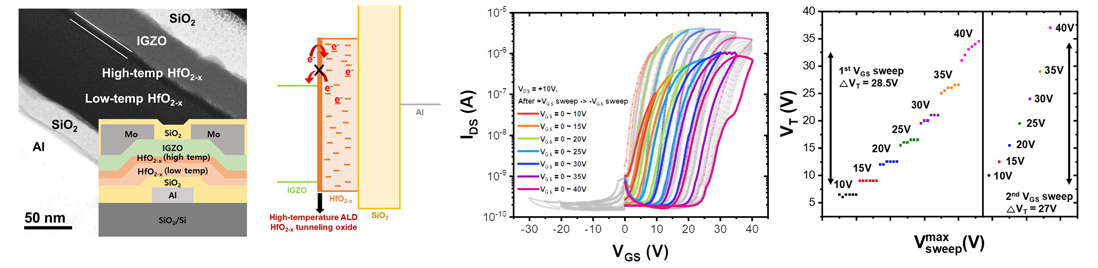

(1) 전하저장에 따른 가중치 변화: 앞서 플래시 메모리와 같이 게이트 절연막 내부의 전하 저장층에 전하를 저장하여 이로 인한 내부 전계에 의해 문턱전압과 채널 전도도를 변화시켜 시냅스 가중치를 변화시킬 수 있다. Seo 등은 MOSFET 구조의 소자에서 게이트 전압에 의해 게이트 절연막 내부의 WOx 전하 저장층과 게이트 전극 간의 전하 이동을 통해 드레인 전류를 아날로그 형태로 조절한 시냅스 특성을 보고하였다[1]. Han 등은 산화물 반도체 박막트랜지스터에서 게이트 절연막 내에 저온에서 원자층증착법으로 증착된 고밀도 트랩을 갖는 HfO2-x 전하 저장층에 저장되는 전하량을 조절하여 가역적이고 점진적인 문턱전압 변화와 채널 전도도를 변화시킨 결과를 보고하였다(그림1)[2].

(2) 강유전체 게이트 절연막의 분극에 의한 가중치 변화: 전하 및 이온 이동 없이 강유전체 게이트 절연막 내부의 분극 현상을 이용해서 채널 전도도 변화가 가능하다. Kim 등은 zirconium-doped hafnium oxide (HfZrOx) 게이트 절연막을 적용한 트랜지스터에 게이트 전압을 인가함에 따라 분극현상으로 인한 채널층 계면에 전하의 축적과 공핍을 유도하여 채널 전도도를 변화시킬 수 있고 이를 시냅스 소자에 적용할 수 있음을 보고하였다[3]. 강유전체 게이트 절연막을 사용할 경우, 전하 및 이온의 이동이 일어나지 않으므로 주변 박막의 열화를 상대적으로 방지할 수 있는 장점이 있으나, 가중치의 선형성, 계면 안정성, 전압 부호에 따른 대칭성을 확보하면서 원치 않는 전하 저장에 따른 성능 저하 등을 억제해야 하는 과제가 남아 있다.

(3) 산산화물 반도체 채널층 내부의 수소 이온 주입에 의한 가중치 변화: 생체 시냅스와 같이 시냅스 내부의 이온 주입과 재분포에 따라 가중치 변화를 구현하는 방법으로서 산화물 반도체 채널층의 도펀트가 되는 수소 이온의 주입 및 이동을 이용하는 방법이다. 수소 이온 주입을 위해서 게이트 절연막 내부에 수소 이온이 포함되도록 박막을 증착하고 게이트 전압에 의해 이를 채널층으로 주입하는 방법이 많이 활용된다. Yang 등은 상부 Au 게이트에 양의 전압 인가를 통해 게이트 절연막으로 활용한 ionic liquid의 내부 수소 이온을 a-MoO3 채널 내부로 주입하여 a-MoO3 채널의 전하 밀도를 증가시켜 채널 전도도를 높였으며, 이러한 수소 이온의 거동이 가역적이면서도 아날로그적인 특성을 보여주었다[4]. 수소 이온을 이용하는 소자는 수소 이온의 높은 이온 이동도로 인하여 저전압 고속 동작에 유리한 반면, 이동한 수소 이온이 쉽게 주변으로 확산함으로써 가중치의 안정성이 낮은 문제를 해결하여야 한다.

(4) 산화물 채널층 내부에 알칼리 이온 주입에 의한 가중치 변화: 내에서 도펀트 역할을 하는 이온으로서 수소 이온과 더불어 알칼리 이온으로서 Li, Na 이온 등이 있으며, 이를 게이트 전압을 이용해서 산화물 반도체 채널층에 주입함으로써 채널층의 전도도 변화가 가능하다. Fuller 등의 연구에서 게이트 전압 인가를 통해 LiCoO2 채널층과 LiPON(lithium phosphorous oxynitride) electrolyte 층 사이의 Li 이온의 이동을 유도하였고, 이를 통해 LiCoO2 채널층 내의 Li의 양을 변조시킴으로써 LiCoO2 채널의 전도도를 아날로그적으로 변화시킴을 보고하였다[5]. Lee 등은 NaWO3 electrolyte 층과 WO3 채널층을 갖는 구조에서 게이트 전압 인가에 따라 n형 도펀트로 역할을 하는 Na 이온의 교환을 통해 채널층 내부의 Na 이온의 농도를 조절하여 아날로그적이면서 대칭적인 시냅스 가중치 변화를 확인하였다[6]. 알칼리 이온을 이용한 소자는 수소 이온을 이용한 소자에 비해 낮은 이동도를 갖지만 상대적으로 높은 안정성을 확보할 수 있다는 장점이 있다. 하지만, 알칼리 이온은 Si CMOS 소자와의 호환성이 낮은 문제가 있다. 시냅스 소자를 Si 기반 뉴런 및 주변 회로와 집적하여야 함으로, 알칼리 이온이 주변 소자를 열화시키지 않도록 하는 것이 필요하다.

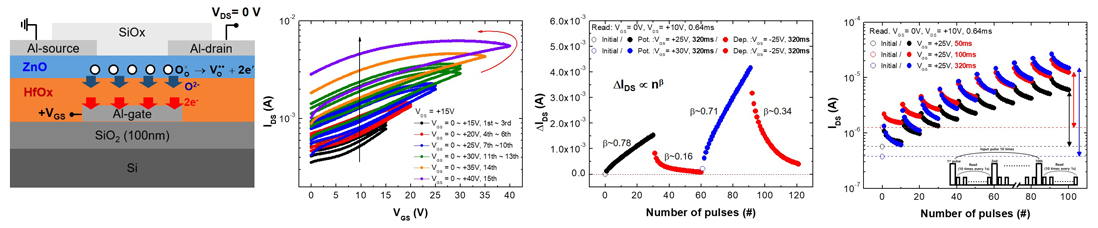

(5) 산화물 반도체 채널층 내부의 산소 이온 재분포에 의한 가중치 변화: 수소 이온, 알칼리 이온과 더불어 산소 공공 또한 산화물 반도체 채널층의 도펀트 역할을 함으로, 산화물 반도체 채널층과 게이트 절연막 사이의 산소 이온 교환을 통해 채널층 내부의 산소 공공 농도의 변화를 유도하고 이를 통해 전도도를 조절하는 방법이다. Jeong 등은 MoOy 이온 저장층과 HfO2 electrolyte 층 그리고 WO3-x 채널층을 가지는 electrochemical ramdom access memory(ECRAM) 소자를 제작하여, 게이트 전압 극성에 따라 WO3-x 채널층과 MoOy 산소 이온 저장층 사이의 산소 이온 교환으로 WO3-x 채널의 전도도를 제어하는 시냅스 소자를 구현하였다[7]. Lee 등은 HfOx 게이트 절연막과 ZnO 산화물 반도체 채널층을 갖는 3단자 시냅스 소자를 제작하여, 게이트 전압에 따라 HfOx 게이트 절연막과 ZnO 채널층 사이의 산소 이온 이동이 일어나서 ZnO 산화물 반도체 내의 n형 도펀트인 산소 공공의 농도가 변하여 채널의 전도도를 변화시킬 수 있었다[8]. 산소 이온 이동에 따른 전도도 변화는 선형적이고 대칭적인 형태를 나타내었으며, 시냅스 소자의 다양한 동작 특성을 구현할 수 있음을 보고하였다[그림2]. 산소 이온을 이용한 소자는 수소 또는 알칼리 이온과 달리, Si CMOS와의 우수한 호환성을 갖고, 재분포한 산소 이온의 장시간 안정성을 확보할 수 있다는 장점이 있으므로 Si CMOS 기반 뉴런 및 주변 소자와의 집적을 통해 뉴로모픽 시스템을 구현하는 것이 가능할 것으로 예상된다. 다만, 산소 이온 이동에 필요한 전압이 상대적으로 높고, 동작 속도가 느리다는 단점이 있으므로 이를 해결하기 위하여 게이트 절연막, 산소 이온 이동층, 산소 이온 저장층, 채널층의 최적화를 통해 뉴로모픽 시스템에 적합한 동작 특성을 확보하는 것이 필요하다.

3. 결론

앞서 설명한 바와 같이, 3단자 시냅스 소자를 구현하기 위하여 다양한 방법이 제안되어 연구되고 있다. 시냅스 소자는 고밀도 뉴런-시냅스 네트워크 구조가 가능해야 하며, 아날로그, 멀티레벨, 선형적, 대칭적 가중치 변화, 우수한 장시간 안정성과 반복 동작 안정성, 시간 의존적 가중치 변화, 높은 에너지 효율과 저전력 구동 등의 소자 성능 지표를 만족하여야 한다. 이와 더불어, Si 소자 및 공정과의 호환성, 신뢰성과 균일성도 함께 확보되어야 한다. 고집적 뉴로모픽 시스템 구현을 위해서 시냅스 소자를 BEOL(Back end of line)에 집적하는 것이 필요하며, 이를 위해서 낮은 공정 온도 조건에서도 우수한 소자 성능이 확보되어야 한다. 하지만, 이러한 모든 소자 성능 지표를 만족하면서 균일성과 신뢰성을 나타내는 소자는 아직 구현되지 못한 상황이다. 일반적인 반도체 소자는 문턱전압, 채널 전도도 등 소자의 전기적 파라미터가 변하지 않고 안정적으로 유지되도록 하는 것이 필요한 반면, 시냅스 소자는 외부에서 전압을 인가하여 소자의 파라미터를 인위적으로 변화시켜야 하는 소자이다. 따라서, 이를 정밀하게 제어하면서 원하는 특성을 얻는 것이 매우 어려운 일이다. 그럼에도 불구하고, 많은 연구자가 시냅스 소자를 구성하는 박막의 물성, 소자 구조, 공정 조건 등을 개선하여 소자의 성능을 지속적으로 개선하고 있다. 따라서, 시냅스 재료, 소자, 공정 엔지니어링을 통해 이를 최적화함으로써 뉴로모픽 시스템에 적용될 수 있는 시냅스 소자가 구현될 수 있을 것으로 기대된다.

참고문헌

[1] Seo, S., Kim, B., Kim, D., Park, S., Kim, T. R., Park, J., Jeong, H., Park, S.-O., Park, T., Shin, H., Kim, M.-S., Choi, Y.-K., Choi, S. (2022). The gate injection-based field-effect synapse transistor with linear conductance update for online training. Nature Communications, 13(1), 6431.

[2] Han, J., Jeong, B., Sahu, D. P., Kim, H. M., & Yoon, T.-S. (2023). Non-volatile charge-trap memory characteristics with low-temperature atomic layer deposited HfO2-x charge-trap layer and interfacial tunneling oxide formed by UV/ozone treatment. Journal of Alloys and Compounds, 951, 169858.

[3] Kim, M. K., & Lee, J. S. (2019). Ferroelectric analog synaptic transistors. Nano Letters, 19(3), 2044-2050.

[4] Yang, C. S., Shang, D. S., Liu, N., Shi, G., Shen, X., Yu, R. C., Li, Y. Q., Sun, Y. (2017). A synaptic transistor based on quasi-2D molybdenum oxide. Advanced Materials, 29(27), 1700906.

[5] Fuller, E. J., Gabaly, F. E., Léonard, F., Agarwal, S., Plimpton, S. J., Jacobs-Gedrim, R. B., James, C. D., Marinella, M. J., Talin, A. A. (2016). Li-ion synaptic transistor for low power analog computing. Advanced Materials, 29, 1604310.

[6] Lee, K., Lee, J., Nikam, R. D., Heo, S., & Hwang, H. (2020). Sodium-based nano-ionic synaptic transistor with improved retention characteristics. Nanotechnology, 31(45), 455204.